- 您现在的位置:买卖IC网 > Sheet目录3871 > PIC18F14K50-I/SO (Microchip Technology)IC PIC MCU FLASH 8KX16 20-SOIC

2010 Microchip Technology Inc.

Preliminary

DS41350E-page 133

PIC18F/LF1XK50

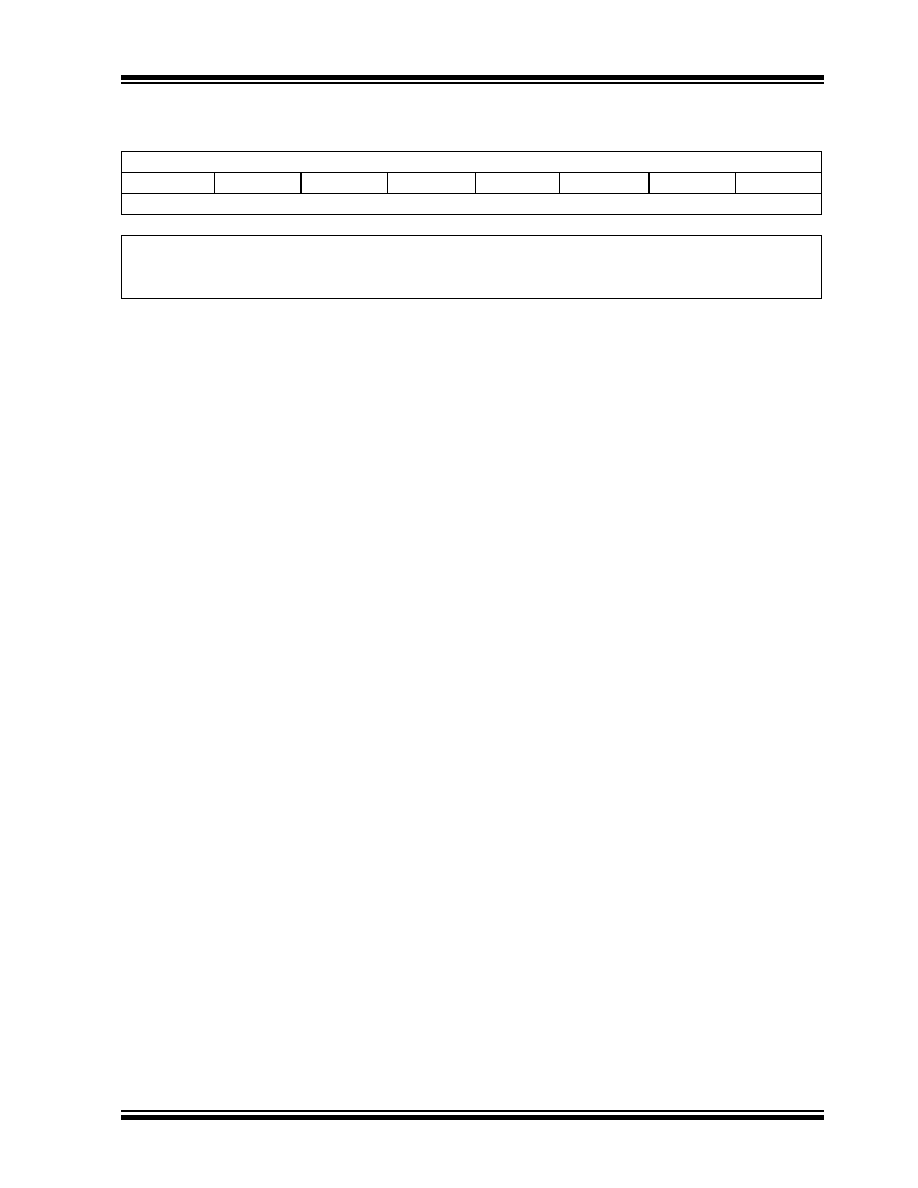

REGISTER 14-3:

PWM1CON: ENHANCED PWM CONTROL REGISTER

R/W-0

PRSEN

PDC6

PDC5

PDC4

PDC3

PDC2

PDC1

PDC0

bit 7

bit 0

Legend:

R = Readable bit

W = Writable bit

U = Unimplemented bit, read as ‘0’

-n = Value at POR

‘1’ = Bit is set

‘0’ = Bit is cleared

x = Bit is unknown

bit 7

PRSEN: PWM Restart Enable bit

1

= Upon auto-shutdown, the ECCPASE bit clears automatically once the shutdown event goes

away; the PWM restarts automatically

0

= Upon auto-shutdown, ECCPASE must be cleared by software to restart the PWM

bit 6-0

PDC<6:0>: PWM Delay Count bits

PDCn = Number of FOSC/4 (4 * TOSC) cycles between the scheduled time when a PWM signal

should transition active and the actual time it transitions active

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

PIC16F628A-I/SS

IC MCU FLASH 2KX14 EEPROM 20SSOP

PIC18LF43K22-I/PT

IC PIC MCU 8KB FLASH 44TQFP

DSPIC33FJ16MC101-I/SO

IC DSP 16BIT 16KB 20SOIC

PIC12C672-04I/SM

IC MCU OTP 2KX14 A/D 8-SOIJ

PIC12C671-04I/SM

IC MCU OTP 1KX14 A/D 8-SOIJ

PIC18F26K20-I/SO

IC PIC MCU FLASH 32KX16 28-SOIC

PIC18LF24J11-I/SO

IC PIC MCU FLASH 16K 2V 28-SOIC

DSPIC33FJ16MC102-I/SS

IC DSP 16BIT 16KB 28SSOP

相关代理商/技术参数

PIC18F14K50-I/SS

功能描述:8位微控制器 -MCU 16KB Flash 768 RAM15 I/O 10-B ADC USB 2.0

RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F14K50T-I/SO

功能描述:8位微控制器 -MCU 16KB Flash 768 RAM15 I/O 10-B ADC USB 2.0

RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F14K50T-I/SS

功能描述:8位微控制器 -MCU 16KB Flash 768 RAM15 I/O 10-B ADC USB 2.0

RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F2220-E/SO

功能描述:8位微控制器 -MCU 4KB 512 RAM 25 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F2220-E/SP

功能描述:8位微控制器 -MCU 4KB 512 RAM 25 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F2220-I/SO

功能描述:8位微控制器 -MCU 4KB 512 RAM 25 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F2220-I/SO

制造商:Microchip Technology Inc 功能描述:IC 8BIT FLASH MCU 18F2220 SOIC28

PIC18F2220-I/SOC03

制造商:Microchip Technology Inc 功能描述: